推 BaaaSwin: 整個迴路應該有包含輸出的gmRc? 變成兩級 03/01 02:53

→ BaaaSwin: 用source follower的形式輸出應該就可以了 03/01 02:56

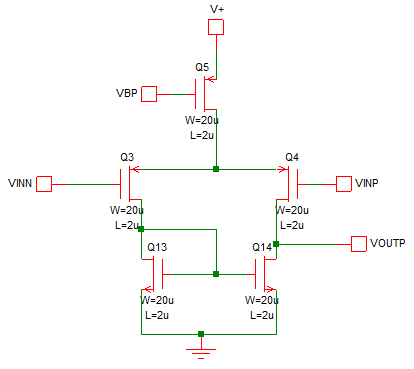

→ blacktea5: 你的正負端有對? 先考慮一下為啥你是-gain 03/01 11:28

→ blacktea5: 你在說的是two stage 的米勒 看不出跟你本身問題的關係 03/01 11:33

→ samm3320: 極性是不是弄錯了 03/01 11:39

不好意思真的弄錯了囧

已經換上正確的圖和敘述

推 blacktea5: 1. 先搞清楚+_-端 和body 2. 搞清楚回授 跟你的gain 03/01 11:41

→ blacktea5: 是正的3. pole 跟zero 4.差cc 把p1p2分離才可以近似 03/01 11:41

→ blacktea5: 米勒 03/01 11:41

→ blacktea5: 你要把 dominate pole 放哪裡 你要決定啊 03/01 11:42

→ blacktea5: 最後 單論 5 mos ota +Cl 確實有zero 但和pole2很近 03/01 11:44

→ blacktea5: 會被消 03/01 11:44

→ blacktea5: 補一下4 你要cs 才有米勒 近似 03/01 11:48

不好意思看不太懂 input pair不算是一種cs嗎?

另外能請教一下5 mos ota的pole2跟zero位置在哪嗎

很多只寫到單一極點由CL決定就結束了...(還是pole2就是我說Q13的G D端?)

※ 編輯: WetDreamZZZ (106.1.235.210 臺灣), 03/01/2022 23:58:06

→ samm3320: 我是覺得你這結構就當2 stage op看就好了 03/02 10:19

→ samm3320: 這沒補償應該穩不下來 03/02 10:20

→ blacktea5: 你第一張圖 的正負端 有對? 第二個ota正負端有對? 3 03/02 11:03

→ blacktea5: 你應該先看為什麼你的gain 是負的 03/02 11:03

→ blacktea5: 看完發現 phase不夠 再來看補償 03/02 11:04

→ samm3320: diff pair的pz 可以看這個教學 03/02 11:07

→ blacktea5: 看看lis 檔 你的dc點 想一下你哪裡沒搞清楚 03/02 11:11

→ cebelas: 大哥你正回授惹,然後你看一個feedback ckt應該是整個loo 03/02 11:15

→ cebelas: p去看,後面就是一個CS amp, Cgd會米勒啊,不過我懷疑你ru 03/02 11:15

→ cebelas: n出來的loop gain 根本操作點也不對, 先算好操作點對了 03/02 11:15

→ cebelas: 再去看這些唄 03/02 11:15